Design overview

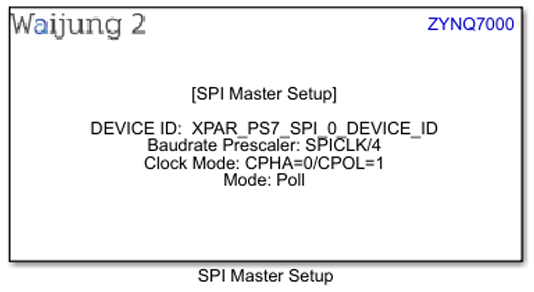

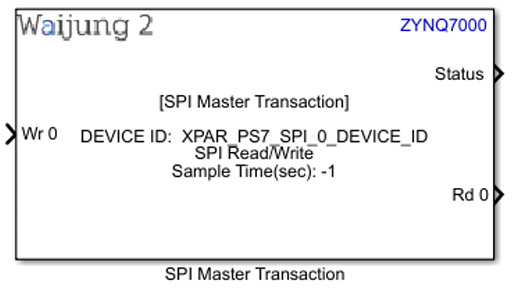

SPI block appearance in a Simulink model,

SPI Setup block

SPI Transaction block

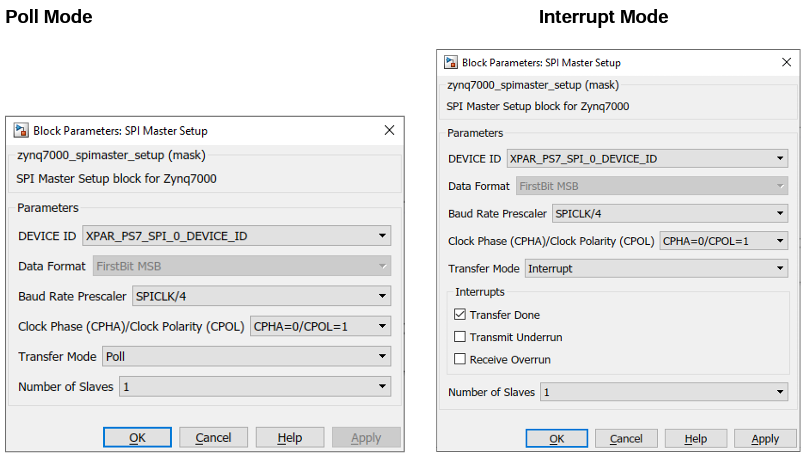

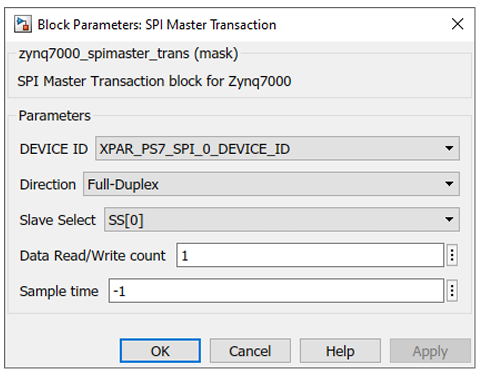

SPI block mask overview,

SPI Setup block

SPI Transaction block

SPI block input interfaces

SPI Transaction block

Name |

Type |

Range |

Description |

All data input ports |

uint8 |

0 - 255 |

Depends on the data configuration of the SPI slave |

SPI block output interfaces

SPI Setup block

Name |

Type |

Range |

Description |

IRQ |

Function-call |

|

This will appear when the Interrupt mode is enabled. Multiple interrupts are represented with a single Function-call output port. To split it to separate ports, use Demux block in Simulink. |

SPI Transaction block

Name |

Type |

Range |

Description |

Status |

uint8 |

0 - 255 |

0: XST_SUCCESS (if the buffers are successfully handed over to the device for transfer.)

21: XST_DEVICE_BUSY (data transfer is already in progress. This is determined by the driver) |

All data output ports |

uint8 |

0 - 255 |

Depends on the data configuration of the SPI slave |

SPI block behavior

SPI block uses the Xilinx SPIPS Driver to perform the SPI communication. SPI pins are configured using ether MIO or EMIO pins. This should be configured using Vivado Design Suite in the design stage. This block supports both Poll and Interrupt modes and in the interrupt mode the interrupt signal(s) will be transferred using Function-call output port.

SPI block configuration

SPI Setup Block

Configuration Parameter |

Selectable Option/Value |

Default Value |

Description |

||||||||

DEVICE ID |

|

Depends on the Hardware design. If both SPI modules are enabled, by default XPAR_PS7_SPI_0_DEVICE_ID is selected |

Depending on the peripheral availability in your hardware design created using the Vivado Design Suite, available device-ids will be shown. |

||||||||

Baud Rate Prescaler |

|

SPICLK/4 |

Prescaler for SPI clock. Clock frequency should be configured using the Vivado Design Suite. This prescaler will be scaled the configured SPI clock frequency. |

||||||||

Clock Phase (CPHA)/Clock Polarity (CPOL) |

|

CPHA=0/CPOL=0 |

CPHA: Clock Phase CPOL: Clock Polarity |

||||||||

Transfer Mode |

|

Poll |

Select Poll or Interrupt mode |

||||||||

Transfer Done |

|

On |

Enable/Disable Transfer Done interrupt by Checking/Unchecking. This will appear when the Transfer mode is Interrupt. |

||||||||

Transmit Underrun |

|

Off |

Enable/Disable Transmit Underrun interrupt by Checking/Unchecking. This will appear when the Transfer mode is Interrupt. |

||||||||

Receive Overrun |

|

Off |

Enable/Disable Receive Overrun interrupt by Checking/Unchecking. This will appear when the Transfer mode is Interrupt. |

||||||||

Number of Slaves |

|

1 |

Number of slaves that are configured in Vivado hardware design. User has to select the slave count according to the Vivado hardware configuration. |

SPI Transaction block

Configuration Parameter |

Selectable Option/Value |

Default Value |

Description |

|||

DEVICE ID |

|

Depends on the Hardware design. If both SPI modules are enabled, by default XPAR_PS7_SPI_0_DEVICE_ID is selected |

Depending on the peripheral availability in your hardware design created using the Vivado Design Suite, available device-ids will be shown. |

|||

Direction |

|

Full-Duplex |

Full-Duplex: use this mode when need to send and receive data at same clock.

Half-Duplex TX: this mode is to transmit data to slave only.

Half-Duplex RX: this mode is to receive data from slave only.

|

|||

Slave Select |

|

SS[0] |

SS[0]: First slave SS[1]: Second slave SS[2]: Third slave Slave select dropdown option will be formed according to the Number Slaves selected from the Setup block. |

|||

Data count |

|

1 |

Number of data ports for the SPI Transaction block. |

|||

Sample time |

|

-1 |

Set the sample time |

SPI block limitation

Typical application

Several demo files are provided at:

[<waijung2 installation directory>\waijung2\targets\zynq7000\demo\spi_demo]

To load the model file run the following commands in the Matlab Command Window:

• Demo: waijung2.openDemoInCurrentFolder('zynq7000', 'spi_demo')